In Internet there seems to be many plans for DIY logic analyzers:

Open source logic analyzer

OpenBench Logic Sniffer

Openbench Logic Sniffer

SUMP FPGA Based Logic Analyzer

FLASH – PLAICE: Programmer, Logic Analyzer and In-Circuit Emulator Project

A logic analyzer using the PC’s parallel port

A logic analyzer using the PC’s parallel port

MiniLA – logic analyzer SW & HW

The “Sump” Logic Analyzer (video demo)

Prototype: Openbench Logic Sniffer logic analyzer

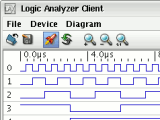

There seems to be many open hardware projects, but what is lacking is good software for them. Some logic analyzer use SUMP PC Client and there is also Java Logic Analyzer Client project (jlac).

I would like to see on this Open Source world is some kind of common format logic analyzer data presentation and maybe common API for accessing the information. In this way it would be easy to write all kinds of applications that decode data and hardware that captures the data independently. It would be easy to integrate different things easily. This would benefit everyone. I would want something like what Wireshark did for network traffic analyzing.

First I though maybe I need to start some of my own code to start this if there is nothing else. For presenting logic data with timestamps one format that come to my mind was Comtrade. Comtrade is a standard for common format for electric power systems transient data exchange. It allows storing many channels of time stamped analogue and digital data. The data is normally in CSV format, so it would be easy to use. There are some standard sample rates but maybe we could use also other rates. Time stamping work at least to microsecond resolution. There are many Comtrade viewing programs, both free and commercial.

Another project that looked interesting was Comedi. The Comedi project develops open-source drivers, tools, and libraries for data acquisition. Comedi is a free software project that develops drivers, tools, and libraries for various forms of data acquisition: reading and writing of analog signals; reading and writing of digital inputs/outputs; pulse and frequency counting; pulse generation; reading encoders; etc. Comedi is a collection of drivers for a variety of common data acquisition plug-in boards in Linux.

I did not go to the trouble of writing my own code for a while. Then about half year ago I saw announcement of Sigrok: An Open Source Logic Analyzer. The sigrok project aims at creating a portable, cross-platform, Free/Libre/Open-Source signal analysis software suite (client) that supports various device types. This was what I was thinking of the end results should be. I start to follow how this project will succeed in their aims. Looks interesting at this point.

25 Comments

ADT San Antonio says:

I’ve read some just right stuff here. Definitely price bookmarking for revisiting. I surprise how much attempt you put to create such a excellent informative web site.

Tomi Engdahl says:

Turning the Stellaris Launchpad into a logic analyzer

http://hackaday.com/2013/01/27/turning-the-stellaris-launchpad-into-a-logic-analyzer/

If you have a Stellaris Launchpad sitting around, have a go at using it as a logic analyzer

This build turns the Launchpad into a 10 MHz, 8-channel logic analyzer with a 16 kB buffer comparable with just about every piece of software thanks to the SUMP protocol.

Open Logic Sniffer software and hardware « Tomi Engdahl’s ePanorama blog says:

[...] (I have not yet tested it with real hardware). The software seem to be considerably getter than some other free logic analyzer software I have checked over years. Logic Sniffer Java client is worth to check out if you are looking for [...]

Tomi Engdahl says:

Comtrade (IEEE Std C37.111-1999) is a common format for electric power systems transient data exchange. It allows storing many channels of time stamped analogue and digital data.

The time stamp has a base unit of microseconds. The elapsed time from the Þrst data sample in a data Þle to the sample marked by any time stamp Þeld in that data Þle is the product of the time stamp for that data sample and the time multiplier in the confguration file (timestamp ´ * timemult).

timemult is the multiplication factor for the time differential (timestamp). It is real numeric value. Typically it is integer (for example 1000 for timestamps in milliseconds).

That timemult can also be in standard floating point notation, meaning more accurate than microsecond time stamps are possible (for example nanoseconds with value 0.001)

boost alexa, like, view says:

I have been browsing on-line more than three hours lately, but I never discovered any attention-grabbing article like yours. It’s lovely price sufficient for me. In my opinion, if all site owners and bloggers made good content material as you probably did, the web can be a lot more helpful than ever before.

Tomi Engdahl says:

ProduinoCY7C68013A-56 USB Logic Analyzer Development Board for Arduino – Blue + Black

http://dx.com/p/produinocy7c68013a-56-usb-logic-analyzer-development-board-for-arduino-blue-black-290156#.UuYFbLSxVaQ

CY7C68013A-56 chipset: Low-power version; Enhanced 51-core; 16KB program data areas; 48MHz frequency

All GPIO are lead out through 2.4mm pin header

Achieve logic analyzer functions with certain firmware

Tomi Engdahl says:

Quite interesting hack:

Turning An Analog Scope Into A Logic Analyzer

http://hackaday.com/2014/04/09/turning-an-analog-scope-into-a-logic-analyzer/

Tomi Engdahl says:

mishmash1 – sdramThing3.0 Logic Analyzer

http://hackaday.io/project/4159-mishmash1-sdramthing30-logic-analyzer

An AVR, a 128MB SDRAM DIMM, an old laptop LCD, and 3 TTL chips make for a 16MS/s multi-channel logic-analyzer interface for an analog ‘scope

Tomi Engdahl says:

SDRAM Logic Analyzer Uses An AVR And A Dirty Trick

http://hackaday.com/2016/03/15/sdram-logic-analyzer-uses-an-avr-and-a-dirty-trick/

We often see “logic analyzer” projects which are little more than microcontrollers reading data as fast as they can, sending it to a PC, and then plotting the results. Depending on how fast the microcontroller is, these projects range from adequate to not very useful.

At first glance, [esot.eric’s] logic analyzer project has an AVR in it, so it ought to be on the low end of the scale. Then you look at the specs: 32 channels at 30 megasamples per second. How does that work with an AVR in it?

The answer lies in the selection of components. The analyzer uses a 128MB SDRAM DIMM (like an older PC might use for main memory). That makes sense; the Arduino can’t store much data internally. However, it isn’t the storage capacity that makes this choice critical. It seems [esot.eric] has a way to make the RAM “free run”.

The idea is to use the Arduino (or other host microcontroller) to set up the memory. Some of the memory’s output bits feedback to the address and data lines. Then the microcontroller steps aside and the SDRAM clocks samples into its memory by itself at the prevailing clock rate for the memory.

sdramThing4.5 “Logic Analyzer”

https://hackaday.io/project/4159-sdramthing45-logic-analyzer

An AVR, 128MB SDRAM DIMM, old laptop LCD, and a handful of TTL chips — 30+MS/s 32-channel logic-analyzer interface for an analog ‘scope

sdramThing4.5 makes it possible to free-run the SDRAM at speeds far-greater than the processor (looking toward 133MHz!).

Once it’s loaded with the initial set of commands, it can be physically disconnected from the MCU and continue doing its thing.

This sample/repeat process is made-possible by sdramThing’s “Free-Running” mode. This mode takes advantage of the SDRAM’s synchronous nature to allow it to control itself.

It’s entirely plausible, with a bit of work, to get sampling up to (and exceeding) the SDRAM’s rated clock-speed of 133MHz (133MS/s). But currently, I’ll be happy to get it working at 40MS/s, as my attempts at decoupling the SDRAM clock from the AVR clock have been slow-in-progress.

Tomi Engdahl says:

Hackaday Prize Entry: The Cheapest Logic Analyzer

http://hackaday.com/2016/07/19/hackaday-prize-entry-the-cheapest-logic-analyzer/

There are piles of old 128MB and 256MB sticks of RAM sitting around in supply closets and in parts bins. For his Hackaday Prize project, [esot.eric] is turning these obsolete sticks of RAM into something useful – a big, fast logic analyzer. It’s cheap, and simple enough that it can be built on a breadboard.

This project is based on [esot.eric]’s earlier AVR logic analyzer project that used a slow AVR to measure 32 channels of logic at 30 megasamples per second.

sdramThingZero – 133MS/s 32-bit Logic Analyzer

https://hackaday.io/project/10119-sdramthingzero-133mss-32-bit-logic-analyzer

Add an old SDRAM DIMM to your SBC for a 133MS/s 32-bit Logic Analyzer, add ADCs for a Scope…

Tomi Engdahl says:

When You Need a Scope, You Need a Scope

http://hackaday.com/2016/08/04/when-you-need-a-scope-you-need-a-scope/

Sometimes there’s just no substitute for the right diagnostic tool. [Ankit] was trying to port some I2C code from an Arduino platform to an ARM chip. When the latter code wasn’t working, he got clever and wrote a small sketch for the Arduino which would echo each byte that came across I2C out to the serial line. The bytes all looked right, yet the OLED still wasn’t working.

ankitdaf/i2c_snoop.ino

Created 15 days ago

https://gist.github.com/ankitdaf/ba7b1326f4d909763effa27201704115

Time to bring out the right tool for the job: a logic analyzer or oscilloscope. Once he did that, the problem was obvious

Tomi Engdahl says:

sdramThingZero – 133MS/s 32-bit Logic Analyzer

https://hackaday.io/project/10119-sdramthingzero-133mss-32-bit-logic-analyzer

Add an old SDRAM DIMM to your SBC for a 133MS/s 32-bit Logic Analyzer, add ADCs for a Scope…

Yes, it likely seems a bit ridiculous to add an old SDRAM DIMM to today’s single-board computers with their whopping e.g. 512MB of onboard DDR2, but believe it or not THERE’S GOOD REASON!!!

Turn your SBC into a logic analyzer, data-logger, or an oscilloscope… You’ll see! Read the Details!

This is a re-envisioning of its “father”, sdramThing4.5:

https://hackaday.io/project/4159-sdramthing45-logic-analyzer

This new revision is more of a peripheral (rather than a complete system) which can be attached to microcontrollers, single-board computers, or even a PC’s parallel-port.

The UI, datalogger, etc. can then be programmed in any language available on the host.

Tomi Engdahl says:

An Open Source 96 MSPS Logic Analyzer For $22

http://hackaday.com/2016/10/26/an-open-source-96-msps-logic-analyzer-for-22/

If you are in the market for an inexpensive USB logic analyser you have a several choices, but few of them deliver much in the way of performance. There are kits from China for a few dollars using microcontrollers at their heart, but they fail to deliver significant sample rates. If you require more, you will have to pay for it.

It is therefore rather interesting to see [kevinhub88]’s SUMP2 project, an open source logic analyser with a claimed 96 MSPS sample rate using an off-the-shelf Lattice iCEstick FPGA evaluation board that only costs about $20. It talks to a host computer via USB using the established SUMP protocol, so its software front-end comes from the sump.org logic analyser project.

Tomi Engdahl says:

$22 FPGA-Based Logic Analyzer Packs a Punch

http://www.eetimes.com/author.asp?section_id=216&doc_id=1330689&

The FPGA-based SUMP2 logic analyzer is useful for large FPGA development, but is also able to scale way down to work on a $22 Lattice iCEstick FPGA+USB board.

Kevin’s latest project is the open source SUMP2 Logic Analyzer — an FPGA-based tool that is useful for large FPGA development, but that is also able to scale way down to work on a $22 Lattice iCEstick FPGA+USB board.

The SUMP2 Logic Analyzer offers 96 MSPS at 16-bits LVCMOS with real-time hardware compression, and the SUMP2 section on the Black Mesa Labs website provides everything you need to get you up and running (apart from the $22 Lattice iCEstick).

So, a big thanks to Kevin for making the SUMP2 available to the community.

SUMP2 – 96 MSPS Logic Analyzer for $22

https://blackmesalabs.wordpress.com/2016/10/24/sump2-96-msps-logic-analyzer-for-22/

Tomi Engdahl says:

sdramThingZero – 133MS/s 32-bit Logic Analyzer

Add an old SDRAM DIMM to your SBC for a 133MS/s 32-bit Logic Analyzer, add ADCs for a Scope…

https://hackaday.io/project/10119-sdramthingzero-133mss-32-bit-logic-analyzer

Yes, it likely seems a bit ridiculous to add an old SDRAM DIMM to today’s single-board computers with their whopping e.g. 512MB of onboard DDR2, but believe it or not THERE’S GOOD REASON!!!

Turn your SBC into a logic analyzer, data-logger, or an oscilloscope… You’ll see! Read the Details!

This is a re-envisioning of its “father”, sdramThing4.5:

https://hackaday.io/project/4159-sdramthing45-logic-analyzer

Tomi Engdahl says:

Compiling a $22 Logic Analyzer

http://hackaday.com/2016/12/13/compiling-a-22-analyzer/

On my way to this year’s Hackaday SuperConference I saw an article on EE Times about someone taking the $22 Lattice iCEstick and turning it into a logic analyzer complete with a Python app to display the waveforms. This jumped out as pretty cool to me given that there really isn’t a ton of RAM on the stick, basically none that isn’t contained in the FPGA itself.

[Jenny List] has also written about the this application as created by [Kevin Hubbard] of Black Mesa Labs and [Al Williams] has a great set of posts about using this same $22 evaluation board doing ground up Verilog design using open source tools. Even if you don’t end up using the stick as a logic analyzer over the long haul, it’ll be very easy to find many other projects where you can recompile to invent a new purpose for it.

SUMP2

[Kevin] refers to his design as SUMP2 and for good reason as there is some departure from the original SUMP architecture. The SUMP2 utilizes a simple lossless compression scheme called Run Length Encoding (RLE) where instead of sending a large number of 0’s or 1’s in a row, it sends a bit value and how many times to repeat that value before the next transition to a different bit state.

An Open Source 96 MSPS Logic Analyzer For $22

http://hackaday.com/2016/10/26/an-open-source-96-msps-logic-analyzer-for-22/

Tomi Engdahl says:

sdramThingZero – 133MS/s 32-bit Logic Analyzer

Add an old SDRAM DIMM to your SBC for a 133MS/s 32-bit Logic Analyzer, add ADCs for a Scope…

https://hackaday.io/project/10119-sdramthingzero-133mss-32-bit-logic-analyzer

Tomi Engdahl says:

Logic Analyzer on Chips

http://hackaday.com/2017/05/17/logic-analyzer-on-chips/

The Internet is full of low-speed logic analyzer designs that use a CPU. There are also quite a few FPGA-based designs. Both have advantages and disadvantages. FPGAs are fast and can handle lots of data at once. But CPUs often have more memory and it is simpler to perform I/O back to, say, a host computer. [Mohammad] sidestepped the choice. He built a logic analyzer that resides partly on an FPGA and partly on an ARM processor.

In fact, his rationale was to replace built-in FPGA logic analyzers like Chipscope and SignalTap. These are made to coexist with your FPGA design, but [Mohammad] found they had limitations. They also eat up die space you might want for your own design, so by necessity, they probably don’t have much memory.

Logic Analyzer

HPS-powered Logic Analyzer debugging FPGA

http://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2017/md874/md874/LogicAnalyzer.htm

Tomi Engdahl says:

BeagleLogic Standalone

BeagleLogic, now as a turnkey and standalone 16-channel Logic Analyzer

https://hackaday.io/project/25745-beaglelogic-standalone

Three years ago, the BeagleLogic project showed how to use a BeagleBone as a 100Msps, 14-channel logic analyzer.

Based on the Octavo Systems’ OSD3358 SIP [BeagleBone on a chip], this is the next step in the evolution of the BeagleLogic project from just an add-on to the BeagleBone to a standalone logic analyzer in itself.

BeagleLogic is not just the hardware, but the software as well. It will feature a new web-based frontend. I am actively learning React and web technologies to be able to build this.

Tomi Engdahl says:

Hackaday Prize Entry: BeagleLogic

http://hackaday.com/2017/07/19/hackaday-prize-entry-beaglelogic/

A few years ago, [Kumar] created the BeagleLogic, a 14-channel, 100 MSPS logic analyzer for the BeagleBone as an entry for the Hackaday Prize. This is a fantastic tool that takes advantage of the PRUs in the BeagleBone to give anyone with a BeagleBone a very capable logic analyzer for not much cash.

This year, [Kumar] is back at it again. He’s improving the BeagleLogic with a BeagleBone on a chip. This is the BeagleLogic Standalone, a 16-channel logic analyzer at 100 MSPS using a single chip.

Tomi Engdahl says:

BeagleLogic Standalone

BeagleLogic, now as a turnkey and standalone 16-channel Logic Analyzer

https://hackaday.io/project/25745-beaglelogic-standalone

Three years ago, the BeagleLogic project showed how to use a BeagleBone as a 100MSa/s, 14-channel logic analyzer.

BeagleLogic Standalone is the next step in the evolution of BeagleLogic from just an add-on to the BeagleBone to a standalone logic analyzer in itself. It is based on the OSD3358 System-In-Package (SiP) from Octavo Systems and increases the specifications to 16-channels @100MSa/s and adds Gigabit Ethernet vs. 100Mbps on the BeagleBone(s).

Tomi Engdahl says:

BeagleLogic Standalone

https://hackaday.io/project/25745-beaglelogic-standalone

BeagleLogic, now as a turnkey and standalone 16-channel Logic Analyzer

Three years ago, the BeagleLogic project showed how to use a BeagleBone as a 100MSa/s, 14-channel logic analyzer.

BeagleLogic Standalone is the next step in the evolution of BeagleLogic from just an add-on to the BeagleBone to a standalone logic analyzer in itself. It is based on the OSD3358 System-In-Package (SiP) from Octavo Systems and increases the specifications to 16-channels @100MSa/s and adds Gigabit Ethernet vs. 100Mbps on the BeagleBone(s).

BeagleLogic standalone is alive and booting! Check out the project logs for more information

Tomi Engdahl says:

A DIY Nine Channel Digital Scope

https://hackaday.com/2018/03/22/a-diy-nine-channel-digital-scope/

Have you ever found yourself in the need of a nine channel scope, when all you had was an FPGA evaluation board? Do not despair, [Miguel Angel] has you covered. While trying to make sense of the inner workings of a RAM controller core, he realized that he needed to capture a lot of signals in parallel and whipped up this 9-channel digital oscilloscope.

The scope is remote-controlled via a JavaScript application, and over Ethernet. Graphical output is provided as a VGA signal at full HD, so it is easy to see what is going on. Downloading sampled data to the controlling computer for analysis is in the works. [Miguel] runs his implementation on an Arty A7 development board which is currently available for around a hundred dollars, but the design is transferable to other platforms. The code and some documentation is available on GitHub

ScopeIO

Embedded Measurement System for FPGA

https://hackaday.io/project/98429-scopeio

Tomi Engdahl says:

https://hackaday.com/2019/05/26/a-modular-logic-analyzer-for-fpgas/

Tomi Engdahl says:

Analog logic analyzer from an STM32 Discovery

https://hackaday.io/project/169193-analog-logic-analyzer-from-an-stm32-discovery

Want to see analog levels as well as digital for 8 channels, without paying the Rigol overlords?