Nowadays you can find many low-cost microcontroller devboards (starting from just few dollars/euros). More recently, we’ve seen ARM Cortex kits for $10-$50, the flowering of the whole Arduino ecosystem, and of course, the Raspberry Pi. It’s microcontroller heaven with very many dev boards available. You you want more performance, there is a wide selection of Linux friendly single board computers in around $35 to $200 range.

What do you want to try next after microcontroller dev boards? Maybe FPGA. A field-programmable gate array (FPGA) is an integrated circuit designed to be configured by a customer or a designer after manufacturing. FPGAs contain programmable logic components called “logic blocks”, and a hierarchy of reconfigurable interconnects that allow the blocks to be “wired together” – somewhat like many (changeable) logic gates that can be inter-wired in (many) different configurations. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR.

Those of us wanting a cheap “in” to the FPGA world have been less lucky than developers looking for microcontroller dev boards. FPGA boards under $100: Introduction article is indicting that the times, they are a changin’. Many FPGA devkits, from both chipmakers and third parties, have broken – or downright shattered – the $100 barrier, opening the door to low-cost FPGA prototyping, education, hobby projects, and so on. FPGA boards under $100: Introduction article offers a good overview of what is available.

Here are some interesting additions to the listed boards:

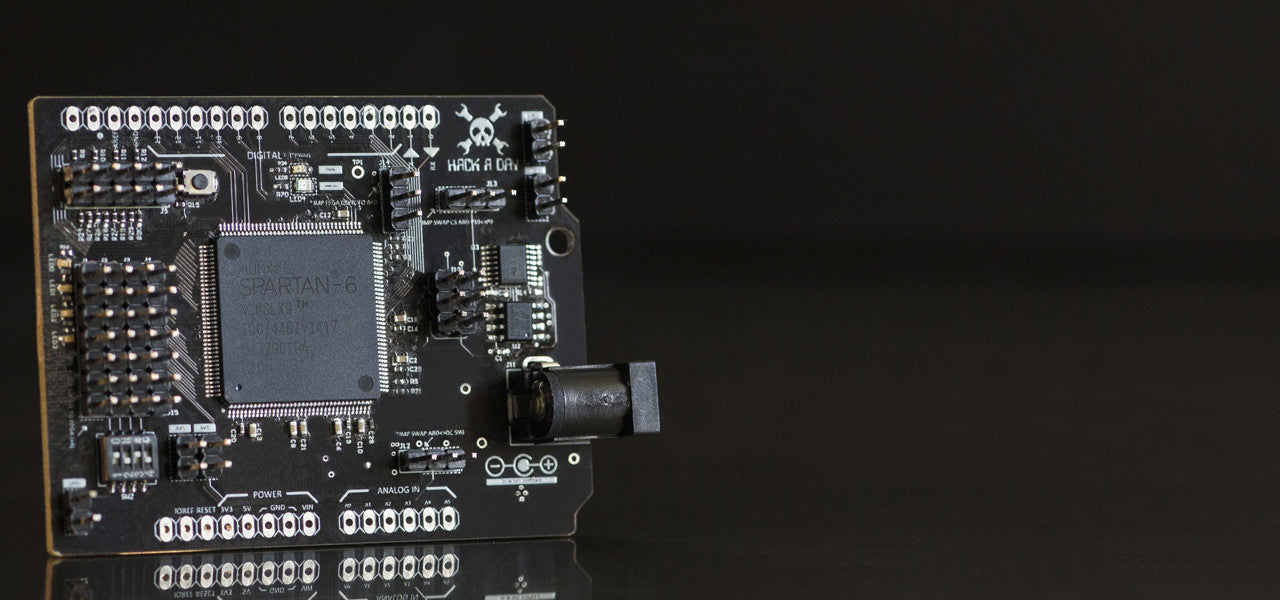

Hacklet 28 – Programmable Logic Hacks posting tells about Arduino-Compatible FPGA Shield. The shield features a Xilinx Spartan 6 FPGA and is available in The Hackaday Store. It has the needed regulators and level shifters. The price is $69.97. Not sure where to start? Check out Spartan-6 FPGA Hello World! that uses Xilinx’s free tool chain to getting a “hello world” led blinker running!

Hacklet 28 – Programmable Logic Hacks posting also mentions Chameleon. Chameleon is an Arduino compatible FPGA board with a Xilinx Spartan 3A FPGA on-board. The Chameleon Arduino-compatible shield board was designed to support two general application areas: (1) soft-core processors, and (2) intelligent serial communications interface.

Cheap FPGA-based HDMI Experimenting Board project is designing a (relatively) cheap little board for experimenting with HDMI using a Spartan-6 FPGA.

432 Comments

Tomi Engdahl says:

From MATLAB and Simulink to FPGAs in Five Easy Steps

https://www.youtube.com/watch?v=yapF8MLWORY

Tomi Engdahl says:

Matlab to VHDL

https://www.youtube.com/watch?v=Oh3gbKr-zy4

using matlab tools to generate VHDL codes

Tomi Engdahl says:

Tech Talk: eFPGA Acceleration

When and why to use embedded FPGAs.

http://semiengineering.com/tech-talk-efpga-acceleration/

Tomi Engdahl says:

A Full Stack GPS Receiver

http://hackaday.com/2017/05/09/a-full-stack-gps-receiver/

The usual way of adding GPS capabilities to a project is grabbing an off-the-shelf GPS module, plugging it into a UART, and reading the stream of NEMA sentences coming out of a serial port. Depending on how much you spend on a GPS module, this is fine: the best modules out there start up quickly, and a lot of them recognize the logical AND in ITAR regulations.

For [Mike], grabbing an off-the-shelf module is out of the question. He’s building his own GPS receiver from the ground up using a bit of hardware and FPGA hacking. Already he’s getting good results, and he doesn’t have to futz around with those messy, ‘don’t build ballistic missiles’ laws.

The hardware for this build includes a Kiwi SDR ‘cape’ for the BeagleBone and a Digilent Nexus-2 FPGA board. The SDR board captures raw 1-bit samples taken at 16.268 MHz, and requires a full minute’s worth of data to be captured. That’s at least 120 Megabytes of data for the FPGA to sort through.

Full Stack GPS Receiver

https://hackaday.io/project/20965-full-stack-gps-receiver

From raw RF samples of the GPS L1 C/A signal to a position fix, in a completely open fashion

Tomi Engdahl says:

‘Flea Ohm’ FPGA Project

https://hackaday.io/project/13048-flea-ohm-fpga-project

Formerly my own raspi-zero style FPGA development board, my Ohm (in Mk2 form) has grown up a bit since then..

Valentin Angelovski

Tomi Engdahl says:

Shift Left Your FPGA Design For Faster Time To Market

http://semiengineering.com/shift-left-your-fpga-design-for-faster-time-to-market/

The need for increased performance leads to an increase in the size and complexity of a design.

In just a few short years, FPGAs have become an integral part of system design for many applications either as a co-processor or the main system processor. As FPGA size and performance increases, system designers are able to utilize them for more tasks. The increased size and performance translates to greater complexity, which is further compounded as designers try to integrate more functionality into a single device.

FPGA Implementation Tools White Paper Download

https://www.synopsys.com/cgi-bin/proto/pdfdla/pdfr1.cgi?file=synplify_shift_left_wp.pdf

Tomi Engdahl says:

Overcome the DC Power Challenge for FPGAs

http://www.electronicdesign.com/power/overcome-dc-power-challenge-fpgas?NL=ED-003&Issue=ED-003_20170515_ED-003_708&sfvc4enews=42&cl=article_1_b&utm_rid=CPG05000002750211&utm_campaign=11074&utm_medium=email&elq2=12f47556f3d142fcb929358d1fdb6fcc

Sponsored by: Texas Instruments. Systems based on FPGAs often require multiple supplies with disparate requirements—a tough problem that can be addressed with dc-dc switching regulators.

Field-programmable gate arrays (FPGAs) have become the go-to component for implementing complex digital designs. Their programmability and flexible features let designers rapidly create functioning prototypes as well as final end products. Some of the latest models include multiple I/O types, NOR flash, analog-to-digital converters (ADCs), digital signal processors (DSPs), and embedded cores that let the designer create sophisticated systems.

FPGAs present their own design challenges for the engineer, but one unexpected issue often crops up in FPGA-based systems design—dc power. The need for multiple supplies of varying requirements

Tomi Engdahl says:

Make Something Awesome with the $99 FPGA-Based Arty Development Board

https://www.eeweb.com/blog/adam_taylor_2/make-something-awesome-with-the-99-fpga-based-arty-development-board

If you are looking to take your first steps into the world of FPGAs, then the Arty and Arty Z7 should be high on your list of development boards to consider.

At $99, the Arty board is ideally placed for both the maker and hobbyist markets. It comes with a 7-series Artix FPGA device from Xilinx, which gives us the ability to create some very interesting design solutions.

When it comes to communicating with the external world, the Arty comes with four Pmod interfaces that can talk to a wide range of peripherals. The Arty board is also equipped with chipKIT / Arduino shield connectors, which allows us to attach a wide range of shields implemented using this popular form factor.

When it comes to creating an application that uses these peripherals, we can either build the application entirely using traditional logic design methods, such as counters, state machines, etc. Alternatively, we can instantiate a 32-bit MicroBlaze soft core processor, which enables us to implement sophisticated control and communication capabilities with greater ease.

Tomi Engdahl says:

Synthesizing Strings on a Cyclone V

http://hackaday.com/2017/05/18/synthesizing-strings-on-a-cyclone-v/

Cornell students [Erissa Irani], [Albert Xu], and [Sophia Yan] built a FPGA wave equation music synth as the final project for [Bruce Land]’s ECE 5760 class.

The team used the Kaplus-Strong string synthesis method to design a trio of four-stringed instruments to be played by the Cyclone V FPGA. A C program running on the development board’s ARM 9 HPS serves as music sequencer, controlling tempo and telling the FPGA which note to play.

Big Red Strings: A FPGA Musical Trio

http://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2017/eli8_sjy33_awx2/ece5760finalproject/ece5760finalproject/index.html

The objective of this project is to implement a musical jukebox on the DE1-SoC. The design made use of both the FPGA and ARM processor. Using the Karplus-Strong algorithm, a number of strings corresponding to three instruments total were synthesized on the FPGA to produce different notes. A C program running on the HPS was responsible for handling file input from a folder containing transcribed sheet music as well as controlling tempo. It also produced a GUI on a VGA display that enables a user to select a preloaded song to play. This system allows music to be read by the HPS and FPGA and synthesize a sound akin to that of a real instrument.

Tomi Engdahl says:

Logic Analyzer on Chips

http://hackaday.com/2017/05/17/logic-analyzer-on-chips/

The Internet is full of low-speed logic analyzer designs that use a CPU. There are also quite a few FPGA-based designs. Both have advantages and disadvantages. FPGAs are fast and can handle lots of data at once. But CPUs often have more memory and it is simpler to perform I/O back to, say, a host computer. [Mohammad] sidestepped the choice. He built a logic analyzer that resides partly on an FPGA and partly on an ARM processor.

In fact, his rationale was to replace built-in FPGA logic analyzers like Chipscope and SignalTap. These are made to coexist with your FPGA design, but [Mohammad] found they had limitations. They also eat up die space you might want for your own design, so by necessity, they probably don’t have much memory.

Logic Analyzer

HPS-powered Logic Analyzer debugging FPGA

http://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2017/md874/md874/LogicAnalyzer.htm

Tomi Engdahl says:

An Education on SoC using Verilog

http://hackaday.com/2017/05/22/an-education-on-soc-using-verilog/

[Bruce Land] is one of those rare individuals who has his own Hackaday tag. He and his students at Cornell have produced many projects over the years that have appeared on these pages, lately with FPGA-related projects. If you only know [Land] from projects, you are missing out. He posts lectures from many of his classes and recently added a series of new lectures about developing with a DE1 System on Chip (SoC) using an Altera Cyclone FPGA using Verilog. You can catch the ten lectures on YouTube.

https://www.youtube.com/watch?v=sKhvMhTiuM4&list=PLKcjQ_UFkrd7UcOVMm39A6VdMbWWq-e_c&index=1

Tomi Engdahl says:

FPGA4Fun a website dedicated to FPGA Development

https://www.eeweb.com/websites/fpga4fun-a-website-dedicated-to-fpga-development

This website has some interesting FPAG projects, tutorials on VHDL and Verilog, as well as a review of some common interfaces.

http://www.fpga4fun.com/

Tomi Engdahl says:

FPGA Rescues Scope From The Dumpster

http://hackaday.com/2017/06/01/fpga-rescues-scope-from-the-dumpster/

Reverse Engineering the LCD Protocols

I only found two perfectly periodic signals: one, a relatively low 31.25 kHz signal gated at a suspicious 60 Hz, and the other a 25 MHz square wave. The former had to be a combined synchronisation signal. The 60 Hz was a dead giveaway as it corresponded to the nominal frame rate. The 31.25 kHz underlying signal must then correspond to the horizontal line rate within a frame. Finally, the 25 MHz signal had to be the clock for the whole system, in fact it was the pixel clock.

Next, I had to make sense of the random-looking signals which were evidently the pixel data.

Clearly this was a standard 640 x 480 display with a refresh rate of 60 Hz.

So exactly, how does one perform the LCD to VGA conversion? With an FPGA of course!

My intention was to, at some point, leave the FPGA inside the scope with the screen, so I needed something small and cheap. Luckily, eBay seems to have a ton of these old Altera Cyclone II based development boards for a mind boggling £10! These are rather capable FPGA’s, hosting about 4K logic elements and ideal for a small scale project like this.

The biggest problem was that the LCD was using 5 V TTL signals. The FPGA can accept at best 3.3 V signals so level conversion had to be performed. I decided to leverage the input clamping diodes in some of the 74HC series logic buffers to perform this conversion

I played it safe and added 1 kΩ series resistors to the input of these buffer and the output of was fed into the FPGA. The output of the FPGA’s HSYNC and VSYNC outputs were hooked up directly to the monitor whilst the RGB lines were connected via 330 Ω resistors.

Tomi Engdahl says:

Hackaday Prize Entry: The FPGA Commodore

http://hackaday.com/2017/06/06/hackaday-prize-entry-the-fpga-commodore/

The history of Commodore 8-bit computers ends with a fantastically powerful, revolutionary, and extraordinarily collectible device. The Commodore 65 was the chicken lip’ last-ditch effort to squeeze every last bit out of the legacy of the Commodore 64. Basically, it was a rework of a 10-year-old design, adding advanced features from the Amiga, but still retaining backwards compatibility. Only 200 prototypes were produced, and when these things hit the auction block, they can fetch as much as an original Apple I.

For their Hackaday Prize entry, resident hackaday.io FPGA wizard [Antti Lukats] and a team of retrocomputing enthusiasts are remaking the Commodore 65. Finally, the ultimate Commodore 8-bit will be available to all. Not only is this going to be a perfect replica of what is arguably the most desirable 8-bit computer of all time, it’s going to have new features like HDMI, Ethernet, and connections for a lot of FPGA I/O pins.

MEGA65 – OPEN 8-BIT COMPUTER

https://hackaday.io/project/11096-mega65-open-8-bit-computer

MEGA65 is an open-source new and open C65-like computer.

Hardware designs and software are open-source (LGPL).

Tomi Engdahl says:

‘Flea Ohm’ FPGA Project

https://hackaday.io/project/13048-flea-ohm-fpga-project

Formerly my own raspi-zero style FPGA development board, my Ohm (in Mk2 form) has grown up a bit since then..

FleaFPGA Ohm/Ohm+ are my own attempts at making a powerful FPGA-based development board in a raspi zero form-factor. This time however, I use the new ECP5 FPGA from Lattice Semiconductor!

I created two new FPGA prototype boards using the capable ECP5 FPGA, which I’ve called the “Ohm” and “Ohm+”.

Tomi Engdahl says:

Quality Assurance Through FPGA

http://hackaday.com/2017/06/10/quality-assurance-through-fpga/

[Claire Chen] and [Mark Zhao], students in [Bruce Land]’s ECE5760 class at Cornell, created a project aimed at the manufacturing sector: quality-checking manufactured products automatically by visually scanning a bunch of them and processing the pixels one at a time. Ordinarily, the time when the widget comes off the line is when you have to bring in actual people to inspect. This project uses morphological image processing to like dilation and erosion to look for flaws.

[Claire] and [Mark] created a simulated manufacturing line with a servo-driven belt that brings a series of Spree candies into the range of a camera, which scans them. The SoC with a Cyclone V FPGA and ARM Cortex-9 then processes the raw images to establish the object’s color, while running it through a couple of algorithms to look for defects.

Counting Spree

http://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2017/yz424_clc288/yz424_clc288/final_website/index.html

Real-Time Vision-based Object Identification and Tracking for Manufacturing Applications

Tomi Engdahl says:

Play FPGA like Arduino

https://hackaday.io/project/20493-play-fpga-like-arduino

Bring open source soft-core MCU into FPGA, enjoy flexibility and customization like no other

As we know, ARM processors are everywhere. The ARM Cortex-M MCUs are widely adopted in embedded systems. However, in addition to this usual approach, the semiconductor industry’s latest juggernaut has made it a viable option, both technically and financially, to embed soft-core MCUs directly into Programmable Logic Chips (FPGA). The latter can be a good alternative to ARM’s dominance, along with the unrivaled flexibility that standalone MCUs cannot offer.

For the open source community, this approach calls for two things:

(1) An open source MCU core that is not burdened by license or patents, and has a large ecosystem (user community, mature tool chains etc.) to make it acceptable to mainstream design.

(2) A platform that hosts the soft-core MCU in (1). This platform shall be open source, versatile, expandable and software friendly, with DFM in mind. So that it can serve as a core module and easily morph into various products.

And here comes PulseRain M10 board!

The PulseRain M10 Board is a versatile and expandable platform that can fit in a wide variety of scenarios

PulseRain M10: A FPGA Board Like No Other

https://www.pulserain.com/m10

we decide to go extra miles and come up with our own board design, which we call M10 board officially. We name it as M10 because:

A) It has an Altera MAX 10 FPGA on board. On the record, M is for MAX

B) It will be the host platform for our FP51-1T soft core MCU. Internally, we nickname FP51 as Mustang to honor the legendary Mustang Fighter-bomber in World War II. So off the record, M stands for Mustang.:-)

We choose Arduino IDE to be our GUI based development environment. Starting V1.5, Arduino IDE has support for 3rd party hardware integration. All you have to do is to point the “Additional Boards URL” to our GitHub repository in “File/Preference/Additional Boards URL”. And then install the board support package in “Tools/Boards/Boards Manager”

Tomi Engdahl says:

You are Go for FPGA!

http://hackaday.com/2017/06/14/you-are-go-for-fpga/

Reconfigure.io is accepting beta applications for its environment to configure FPGAs using Go. Yes, Go is a programming language, but the software converts code into FPGA constructs, so you don’t need Verilog or VHDL. Since Go supports concurrent routines and channels for synchronization and communications, the parallel nature of the FPGA should fit well.

There is a bit more detail, however, on their GitHub site.

We’ve seen C compilers for FPGAs (more than one, in fact). You can also sort of use Python. Is this tangibly different? It sounds like it might be

Program FPGAs with Go

https://reconfigure.io/

Reconfigure.io brings the power of hardware-acceleration technology to the cloud ecosystem. Code in Go, and easily build, test and deploy to FPGAs in the cloud.

Tomi Engdahl says:

Open Source Digital Cinema

http://hackaday.com/2017/06/17/open-source-digital-cinema/

Years in the making, Apertus has released 25 beta developer kits for AXIOM–their open source digital cinema camera. This isn’t your point-and-shoot digital camera. The original proof of concept from 2013 had a Zynq processor (a Zedboard), a super 35 4K image sensor, and a Nikon F-Mount.

The device today is modular with several options. For example, there is an HDMI output module, but DisplayPort, 4K HDMI, and USB 3.0 options are in development. You can see several sample videos taken with the device, below.

The current device uses a Cmosis CMV12000 image module, although a Kodak KAC12040 and Cmosis CMV2000 module are in the works. You can find the complete specs online, but be aware that some of these specifications are forward-looking. On the other hand, the videos clearly show it is in a working state.

If you’ve been looking for an open source FPGA or microcontroller project to hook up with, this might be it. Like a lot of open source companies, they are trying to commercialize to keep the project healthy

Building a new camera prototype from scratch: AXIOM Alpha

https://www.apertus.org/history

Tomi Engdahl says:

Voice Shifting with a Cyclone V FPGA

http://hackaday.com/2017/06/18/voice-shifting-with-a-cyclone-v-fpga/

Cornell Students [Sean Carroll], [Gulnar Mirza], and [James Talmage] designed a realtime pitch shifter to run on their DE1-SoC and controlled by its ARM core.

The team’s goals were to pitch-shift the left and right outputs independently, to produce chords using the original voices as well as the pitch-shifted ones, and time-delayed pitch shifting. All of it is controlled on a VGA monitor through a simple GUI, allowing users to create lots of different effects by layering the different options.

PitchShifter

Change the pitch of your voice in real-time!

http://people.ece.cornell.edu/land/courses/ece5760/FinalProjects/s2017/jmt329_swc63_gzm3/jmt329_swc63_gzm3/PitchShifter/index.html

Tomi Engdahl says:

Mouser – Pocket-sized logic analyzer and pattern generator in a single instrument (Digilent 410-338)

http://www.electropages.com/2017/06/mouser-pocket-sized-logic-analyzer-pattern-generator-single-instrument/?utm_campaign=2017-06-26-Electropages&utm_source=newsletter&utm_medium=email&utm_term=article&utm_content=Mouser+-+Pocket-sized+logic+analyzer+and+pattern+generator+in+a+single+…

Mouser is now stocking the Digital Discovery module from Digilent. This pocket-sized, high-performance device combines a logic analyzer and built-in pattern generator in a single instrument. The Digital Discovery provides designers a suite of advanced features to debug, visualize and simulate digital signals for a broad array of embedded projects. The small form factor of this module facilitates easy storage, and its robust exterior design helps it to withstand a variety of environments.

The device evaluates the Xilinx XC6SLX25-2 FPGA. In addition to the 16-channel pattern generator and 32-channel digital logic analyzer, the module includes a protocol analyzer for reading and writing SPI, UART and I2C and virtual I/O for debugging projects.

The module offers the flexibility to customize design specifications to a specific project, enabling designers to choose 200MS/s with up to 32 inputs or — using the high speed adapter — 400MS/s with up to 16 inputs, or 800MS/s with up to eight inputs.

Tomi Engdahl says:

FPGAs 1, MCUs 0

https://www.eeweb.com/blog/max_maxfield/fpgas-1-mcus-0

The fact that FPGAs can attack appropriate algorithms in a massively parallel fashion can be extremely efficacious in certain circumstances.

One of the guys in my office building is overly-enthused by traditional computational engines in the form of microprocessors (MPUs) and microcontrollers (MCUs). He’s convinced himself that they offer the best possible solution for almost any computational problem, and the bounder even went so far as to offer some rather disparaging opinions regarding the efficacy of field-programmable gate arrays (FPGAs).

Now, don’t get me wrong, I love playing with MCUs. The bay outside my office is filled to bursting with a bewildering and bedazzling assortment of Arduino-powered artifacts. I’m happy to state for the record that traditional processor architectures are wonderful when it comes to performing decision-making, control-type activities. However, it also needs to be acknowledged that they can be horrendously, power-guzzlingly inefficient when it comes to performing certain data-crunching tasks.

By comparison, the fact that FPGAs can attack appropriate algorithms in a massively parallel fashion can be extremely efficacious in certain circumstances.

I think I have the perfect test case to illustrate the differences between MCUs and FPGAs when it comes to solving a certain class of problems. Are you familiar with the Game of Life? This is a cellular automaton that was devised by the British mathematician John Horton Conway in 1970.

Theoretically, the Game of Life universe is infinite. In practice, it’s common to set some sort of bounds, like a 1,000 × 1,000 array, to accommodate its being displayed on a computer screen, for example. In this case, it’s common to visualize the edges of the universe as “wrapping around” such that the top edge “meets” the bottom edge and the left-hand side “meets” the right-hand side.

Tomi Engdahl says:

RGGber Embedded Vision Development Kit

https://www.crowdsupply.com/jie-zou/rggber-dev-kit

A fully open source, affordable, modular development kit that makes embedded vision development easy.

RGGBer is a complete dev-kit dedicated to the embedded vision domain. It is based on an FPGA and provides all the necessary hardware resources to support 1080p @ 60 Hz video applications.

RGGBer helps you quickly start your video or digital image projects with various modular boards and accessories, so you can tailor the hardware to your project.

Crowd Supply

RGGber Embedded Vision Development Kit

A fully open source, affordable, modular development kit that makes embedded vision development easy.

This project is coming soon. Sign up to receive updates and be notified when this project launches.

[email protected]

Subscribe

RGGBer Dev Kit

Overview

RGGBer is a complete dev-kit dedicated to the embedded vision domain. It is based on an FPGA and provides all the necessary hardware resources to support 1080p @ 60 Hz video applications.

RGGBer helps you quickly start your video or digital image projects with various modular boards and accessories, so you can tailor the hardware to your project. This lets you save time and money by freeing you from having to do general PCB design and construction. It also saves time and money by letting you choose from well developed FPGA framework and reference designs.

In keeping with principles of open hardware, all documentation regarding the FPGA framework, high quality reference designs, etc., will be freely available on GitHub.

Features and Specifications

FPGA processor board

FPGA chip: EP4CE30F23C6N/C8N

DDR2 chips: 2 x MT47H64M16HR

USB 2.0 to UART bridge: CP2102-GM

10 pin JTAG port

2 x 100 pins high speed expansion connectors

68 mm x 60 mm

Image mainboard

HDMI RX chip: TFP401APZP, video only, pixel rate 165 Mhz, 1080p and WUXGA at 60 Hz, RGB 24 bits

HDMI TX chip : TFP410PAP, video only, pixel rate 165 Mhz, 1080p and WUXGA at 60 Hz, RGB 24 bits

BLE4.0 to UART module for wireless control

On board MCU

You can access and control RGGBer via our Android app.

Tomi Engdahl says:

VexRiscv: A Modular RISC-V Implementation for FPGA

http://hackaday.com/2017/07/21/vexriscv-a-modular-risc-v-implementation-for-fpga/

Since an FPGA is just a sea of digital logic components on a chip, it isn’t uncommon to build a CPU using at least part of the FPGA’s circuitry. VexRiscv is an implementation of the RISC-V CPU architecture using a language called SpinalHDL.

SpinalHDL is a high-level language conceptually similar to Verilog or VHDL and can compile to Verilog or VHDL, so it should be compatible with most tool chains. VexRiscv shows off well in this project since it is very modular. You can add instructions, an MMU, JTAG debugging, caches and more.

When you build a CPU in FPGA, you generally have to make one of three choices. You can roll your own, which is great fun but requires a lot of work both on the design and the associated tools, for example, a cross-compiler or operating system. You can “borrow” an existing architecture or design which may or may not be legal, depending on what you pick. You can also use a commercial offering. While some of these are free in some circumstances, you’ll pay for anything substantial.

This open implementation offers you an easy way to leverage some great tools. There’s a debugging interface for GDB and a FreeRTOS port. You have a 32-bit part that can achieve 1.16 Dhrystone MIPS/MHz even with all features turned on. This is comparable to commercial 32-bit processors.

A FPGA friendly 32 bit RISC-V CPU implementation

https://github.com/SpinalHDL/VexRiscv

Tomi Engdahl says:

Game Gear HDMI with SNES Controller

http://hackaday.com/2017/07/23/game-gear-hdmi-with-snes-controller/

With its backlit color screen and Master System compatibility, the Game Gear was years ahead of its main competition. The major downside was that it tore through alkaline batteries quickly, and for that reason the cheaper but less equipped Game Boy was still able to compete. Since we live in the future, however, the Game Gear has received new life with many modifications that address its shortcomings, including this latest one that adds an HDMI output.

The core of the build is an FPGA which is used to handle pixel decoding and also handles the HDMI output. The FPGA allows for a speed high enough to handle all the data that is required,

Tomi Engdahl says:

‘Flea Ohm’ FPGA Project

My attempt at making an FPGA experimenters board in a popular form factor

https://hackaday.io/project/13048-flea-ohm-fpga-project

FleaFPGA Ohm/Ohm+ are my own attempts at making a powerful FPGA-based development board in a raspi zero form-factor. This time however, I use the new ECP5 FPGA from Lattice Semiconductor!

Tomi Engdahl says:

Play FPGA like Arduino

You can make a Lego Monster Truck out of it!

https://hackaday.io/project/20493-play-fpga-like-arduino

Over the past 10 years, FPGA (Field Programmable Gate Array) device has grown into main stream, with its capacity surging and the unit cost dropping. Instead of using a hardcore MCU, embedding a soft-core MCU into FPGA, with all the peripherals customized, is now within the reach of makers. And that’s where PulseRain M10 comes into play, an open source design down to the silicon level!

The M10 board takes a distinctive technical approach by embedding an open source soft MCU core (96MHz) into an Intel MAX10 FPGA, while offering an Arduino compatible software interface and form factors. Introducing M10 board into the maker market will bring flexibility and expandability that current solutions (Raspberry Pi and Arduino) cannot offer.

The M10 board can serve as a core module and easily morph into various cool things. For starters, you can build a Lego Monster Truck out of it!

Tomi Engdahl says:

TinyFPGA is a Tiny FPGA Board

http://hackaday.com/2017/07/31/tinyfpga-is-a-tiny-fpga-board/

We recently noticed an open source design for TinyFPGA A-Series boards from [Luke Valenty]. The tiny boards measure 18 mm by 30.5 mm and are breadboard friendly. You can choose a board that holds a Lattice Mach XO2-256 or an XO2-1200, if you need the additional capacity.

The boards have the JTAG interface on the side pins and also on a top header that would be handy to plug in a JTAG dongle for programming.

https://hackaday.io/project/25958-tinyfpga-a-series

Tomi Engdahl says:

The Coming of the Age of the Maker FPGA Board

https://blog.hackster.io/the-coming-of-the-age-of-the-maker-fpga-board-52a29572549e

Field-programmable gate arrays (FPGAs) are a very different to a regular microcontroller board. With a microcontroller you have control over is the software, the code that runs on the chip, but with an FPGA you start with a blank slate and design the circuit rather than write the code that runs on it. There is no processor to run software, at least not until you design it.

A number of FPGA boards targeting the maker market — like Alorium’s XLR8 for instance — are starting to appear, and among them is a new range of open source TinyFPGA boards.

Tomi Engdahl says:

HDL training board by FPGA for real beginner

Previously I’ve made CPLD board, but eventually new FPGA version!

https://hackaday.io/project/26175-hdl-training-board-by-fpga-for-real-beginner

From view point of user experience, CPLD and FPGA (with flash) are almost identical just for writing HDL. But recent FPGA has several built-in module such as I2C and SPI and it leads to good possibility to make “original I2C chip” or “original SPI chip”. This time I made a FPGA training board by Lattice’s MachO2-256, which has both I2C and SPI “ready-made” module inside and suitable for such purpose. I know the vendor (Lattice) has a product of “$30 break-out board” but we need to add several SW and LED just for initial testing. This board has embedded programmer by FTDI FT232HL, five tactile SWs, two 7-seg LEDs and one buffer amp for Piezo sounder. As same as my previous Xilinx 9572XL based board, this board as very low frequency time base, from 8 Hz (not kHz) to 2048 Hz and those are injected to FPGA. This board is not for professional but beginner. This board has good possibility…!

Tomi Engdahl says:

Collection of Arduino Tutorials

https://hackaday.io/project/7562-collection-of-arduino-tutorials

Tomi Engdahl says:

ArdupilotTiny

Run Ardupilot Scheduler on atmega328p Arduino.

https://hackaday.io/project/13235-ardupilottiny

Tomi Engdahl says:

TinyFPGA Programmer

A dirt cheap open hardware USB-JTAG board designed to program TinyFPGA A1 and A2 boards.

https://hackaday.io/project/26836-tinyfpga-programmer

View Gallery

0

18

11

Team (1)

Luke Valenty

Join this project’s team

TinyFPGA Programmer Repository

TinyFPGA A-Series Project

hardware

ongoing project

JTAG pic FPGA usb

This Project Is In This List

Projects using OSHpark boards

Browse all lists »

This project was created on 08/16/2017 and last updated 3 hours ago.

Description

One of the goals of the TinyFPGA boards is to make FPGAs cheaper to use. The #TinyFPGA A-Series boards are the first TinyFPGA boards and are designed to be the least expensive. As such, they do not include a built-in USB interface as that would increase the cost and complexity too much. Instead they rely on JTAG programmers.

There are many Lattice Diamond compatible JTAG programmers available on eBay for $20 or so that will do the job. However, it would be nice to have a less expensive open-source option designed for the TinyFPGA A-Series boards.

Here comes the TinyFPGA Programmer. Rather than an FTDI2232 USB interface chip it uses a PIC16F1455 USB microcontroller. While not compatible with the FTDI2232 chip, the PIC micro has a much lower BOM cost allowing the programmer hardware to be cheaper. The raw cost of the board should be just a few US dollars. It should be possible to sell fully-assembled programmer boards for less than $10.

I started development of the Python module for interfacing with the programmer hardware. Currently the module reads a standard SVF file from the Lattice tools and attempts to play back all the commands over JTAG.

Started using the MPLAB debugger tools, pretty slick stuff. But it sure looks silly having the PIC programmer stacked on top of the FPGA programmer stacked on top of the FPGA board:

Tomi Engdahl says:

Beginner’s Guide to Understanding FPGA Development

https://www.eeweb.com/blog/gina_smith/beginners-guide-to-understanding-fpga-development

Tomi Engdahl says:

TinyFPGA B-Series

https://hackaday.io/project/26848-tinyfpga-b-series

Low-cost, open-source FPGA boards in a tiny form factor with built-in USB, SPI flash, LDO, and MEMS clock.

The TinyFPGA B-Series boards continue the philosophy of the A1 and A2 boards but with more FPGA resources and integrated functions on the board. Unlike the A-Series, the B-Series includes a 16MHz clock, voltage regulators, 4MBit SPI flash, and programming over USB.

Instead of using a separate USB interface chip the B-Series boards implement a USB bootloader that is able to reprogram the user configuration bitstream into the SPI flash. The bootloader automatically reboots the FPGA with the user configuration. Once the user configuration is running the bootloader no longer consumes any FPGA resources.

Tomi Engdahl says:

Retrocomputing With Open Source FPGAs

http://hackaday.com/2017/08/28/retrocomputing-with-open-source-fpgas/

A few years ago, we saw the reverse engineering of the Lattice iCE40 bitstream, opening the door to a completely Open Source development tool chain for FPGAs. This was an astonishing amount of work from [Clifford Wolf], [Mathias Lasser], and [Cotton Seed], but since then we haven’t seen a whole lot from Project IceStorm. Now, that’s about to change, and in the coolest way possible. [hoglet] is retrocomputing on an ICE40 development board.

This is an implementation of the Acorn Atom on a myStorm BlackIce board. This board is basically just a Lattice iCE40 FPGA, a few support components, and a bunch of pin headers, some of which are in the not-so-handy Arduino pinout footprint. By porting some Acorn Atom implementations and a 6502 core to verilog, [hoglet] was able to stuff a cool old retrocomputer onto an Open Source FPGA development board. Video output is through a resistor DAC driving a VGA cable, and keyboard input is through PS/2.

Acorn Atom implementation for myStorm BlackIce

https://forum.mystorm.uk/t/acorn-atom-implementation-for-mystorm-blackice/228

Tomi Engdahl says:

Improve FPGA project management/test by eschewing the IDE

http://www.edn.com/design/integrated-circuit-design/4458754/Improve-FPGA-project-management-test-by-eschewing-the-IDE

1 Introduction

A common way to do an FPGA design is to create a project using your design tool. A project consists of a hierarchy of directories and many files. Creating a project, you have a nice GUI, wizards, and you can even create your design without touching your keyboard – with mouse clicks only. It works well for small and simple projects, or projects where you only combine existing IPs in a purpose-specific mixture.

Unfortunately, in larger projects – with tons of code – this project-centered approach creates significant problems, such as with attempts to use source code control systems (SCCS), test-driven development techniques, or any other systematic testing methodology.

Using design tools in non-project mode eliminates these problems.

Tomi Engdahl says:

TinyFPGA Programmer

https://hackaday.io/project/26836-tinyfpga-programmer

A dirt cheap open hardware USB-JTAG board designed to program TinyFPGA A1 and A2 boards.

Tomi Engdahl says:

CPLD Fun Board

https://hackaday.io/project/27062-cpld-fun-board

Homemade low cost CPLD dev board (Arduino STM32F103 and Altera MAX II EPM240 CPLD)

Two dev boards in one: a STM32 based Arduino and an Altera MAX II CPLD dev board to start playing with VHDL/Verilog, or just to try to use a CPLD with the Quartus II schematic editor. The cost should be about 5/6$ plus the PCB (I haven’t done the precise BOM calculation yet…), buying the components “around”. The “pluggable” LCD module and the optional stand-alone 50MHz oscillator aren’t included in the cost count.

Tomi Engdahl says:

Tech Talk: eFPGA Test

How to plan for sufficient coverage for an embedded FPGA and how much it will cost.

https://semiengineering.com/tech-talk-efpga-test/

Tomi Engdahl says:

TinyFPGA Programmer

A dirt cheap open hardware USB-JTAG board designed to program TinyFPGA A1 and A2 boards.

https://hackaday.io/project/26836-tinyfpga-programmer

Tomi Engdahl says:

Demystifying AXI Interconnection for Zynq SoC FPGA

Analyzing the interface between the processing unit and programmable logic in the Zynq architecture

https://www.aldec.com/en/company/blog/145–demystifying-axi-interconnection-for-zynq-soc-fpga

Imagine traveling back in the time to the early human ages. It’s going to be both scary and interesting when you meet a person who probably cannot speak or if they do you won’t be able to understand them. Clearly, communication will not be possible until you find a mutual way to convey your respective meanings/intentions. The same principle applies in the world of electronics as there are various types of interfaces among electronic devices. Therefore, a standard communication protocol eases the transformation of data in a system, especially in a System-on-Chip (SoC) system which consists of different systems.

SoC FPGAs such as Xilinx® Zynq™ establishes the ARM Advanced Microcontroller Bus Architecture (AMBA) as the on-chip interconnection standard to connect and manage the functional blocks within the SoC design. The Advanced eXtensible Interface (AXI) is designed for FPGAs based on AMBA as a protocol for communication between blocks of IP.

Tomi Engdahl says:

FPGA Clocks for Software Developers (or Anyone)

https://hackaday.com/2017/09/21/fpga-clocks-for-software-developers-or-anyone/

It used to be that designing hardware required schematics and designing software required code. Sure, a lot of people could jump back and forth, but it was clearly a different discipline. Today, a lot of substantial digital design occurs using a hardware description language (HDL) like Verilog or VHDL. These look like software, but as we’ve pointed out many times, it isn’t really the same. [Zipcpu] has a really clear blog post that explains how it is different and why.

[Zipcpu] notes something we’ve seen all too often on the web. Some neophytes will write sequential code using Verilog or VHDL as if it was a conventional programming language. Code like that may even simulate. However, the resulting hardware will — at best — be very inefficient and at worst will not even work.

We did mildly disagree with one statement in the post: “…no digital logic design can work without a clock.”

Clocks for Software Engineers

http://zipcpu.com/blog/2017/09/18/clocks-for-sw-engineers.html

Tomi Engdahl says:

A Cold Hard Look at FPGAs

https://hackaday.com/2017/09/25/a-cold-hard-look-at-fpgas/

Researchers at the Delft University of Technology wanted to use FPGAs at cryogenic temperatures down around 4 degrees Kelvin. They knew from previous research that many FPGAs that use submicron fabrication technology actually work pretty well at those temperatures. It is the other components that misbehave — in particular, capacitors and voltage regulators. They worked out an interesting strategy to get around this problem.

The common solution is to move the power supply away from the FPGA and out of the cold environment.

FPGA Design Techniques for Stable Cryogenic Operation

https://arxiv.org/pdf/1709.04190.pdf

Tomi Engdahl says:

The Linux FPGA

https://hackaday.com/2017/09/26/the-linux-fpga/

It was never unusual to have a CPU and an FPGA together. After all, each has different strengths and weaknesses. However, newer devices like the Xilinx Zynq have both a CPU and an FPGA in the same package. That means your design has to span hardware, FPGA configurations, and software. [Mitchell Orsucci] was using a Zynq device on a ArtyZ7-20 board and decided he wanted to use Linux to operate the ARM processor and provide user-space tools to interface with the FPGA and reconfigure it dynamically.

Interfacing with an FPGA from Linux on ZYNQ

https://www.hackster.io/morsucci/interfacing-with-an-fpga-from-linux-on-zynq-90ea3e

Control an FPGA from the Linux OS. Dynamically reconfigure the FPGA from Linux user-space. Control custom hardware on the FPGA from Linux.

Tomi Engdahl says:

The Hobbyists Guide to FPGAs

https://hackaday.io/project/27550-the-hobbyists-guide-to-fpgas

Follow this project to learn how to use FPGAs and incorporate them into your projects.

Tomi Engdahl says:

Basics Of Embedded FPGA Acceleration

Why programmability is essential for speeding up SoC performance.

https://semiengineering.com/basics-of-embedded-fpga-acceleration/

Making a chip run faster is no longer guaranteed by shrinking features or moving to a different manufacturing process. It now requires a fundamental change in the architecture of the chip itself.

The days of the single-processor, or even single multi-core processors, are gone. The focus has shifted to different kinds of processors for different kinds of data and many different protocols and I/O schemes. Some of these are still being developed.

Embedded FPGAs are a new way of adding speed with flexibility. In the past, a common strategy was to embed a processor within an FPGA. It turns out the reverse is a much more efficient solution to the problem, embedding the FPGA within a chip that can both accelerate a variety of operations without facing obsolescence by the time the chip reaches production. In a variety of new markets such as machine learning, AI and automotive, programmability is the best approach.

Tomi Engdahl says:

Tech Talk: eFPGA Verification

How embedded FPGAs compare to a discrete FPGAs and ASICs.

https://semiengineering.com/tech-talk-efpga-verification/

Chris Pelosi, vice president of hardware engineering at Achronix, explains how to verify an embedded FPGA, and how that compares with verification of discrete FPGAs and ASICs.

Tech Talk: eFPGA Verification

https://www.youtube.com/watch?v=UBLNabLUg9I

Tomi Engdahl says:

TinyFPGA B-Series

https://hackaday.io/project/26848-tinyfpga-b-series

Low-cost, open-source FPGA boards in a tiny form factor with built-in USB, SPI flash, LDO, and MEMS clock.

Tomi Engdahl says:

TinyFPGA A-Series

Low-cost, open-source FPGA boards in a tiny form factor.

https://hackaday.io/project/25958-tinyfpga-a-series

The TinyFPGA A-Series boards are tiny bare-bones FPGA boards with a low cost per logic element. They are programmed via their built-in JTAG interface and only contain the bare-minimum of components for the FPGA to function. They measure 18mm x 30.5mm and fit well in breadboards.

TinyFPGA Programmer

A dirt cheap open hardware USB-JTAG board designed to program TinyFPGA A1 and A2 boards.

https://hackaday.io/project/26836-tinyfpga-programmer